## Содержание

| ВВЕДЕНИЕ                                                         | 3  |

|------------------------------------------------------------------|----|

| 1 ТЕОРЕТИЧЕСКИЙ РАЗДЕЛ                                           | 4  |

| 1.1 Структурная схема процессора со схемной логикой              | 4  |

| 1.2 Понятие цифрового автомата                                   | 6  |

| 1.3 Анализ блок-схемы алгоритма команд                           | 8  |

| 1.4 Определение состояний устройства управления и их кодирование | 8  |

| 2 ПРАКТИЧЕСКИЙ РАЗДЕЛ                                            | 13 |

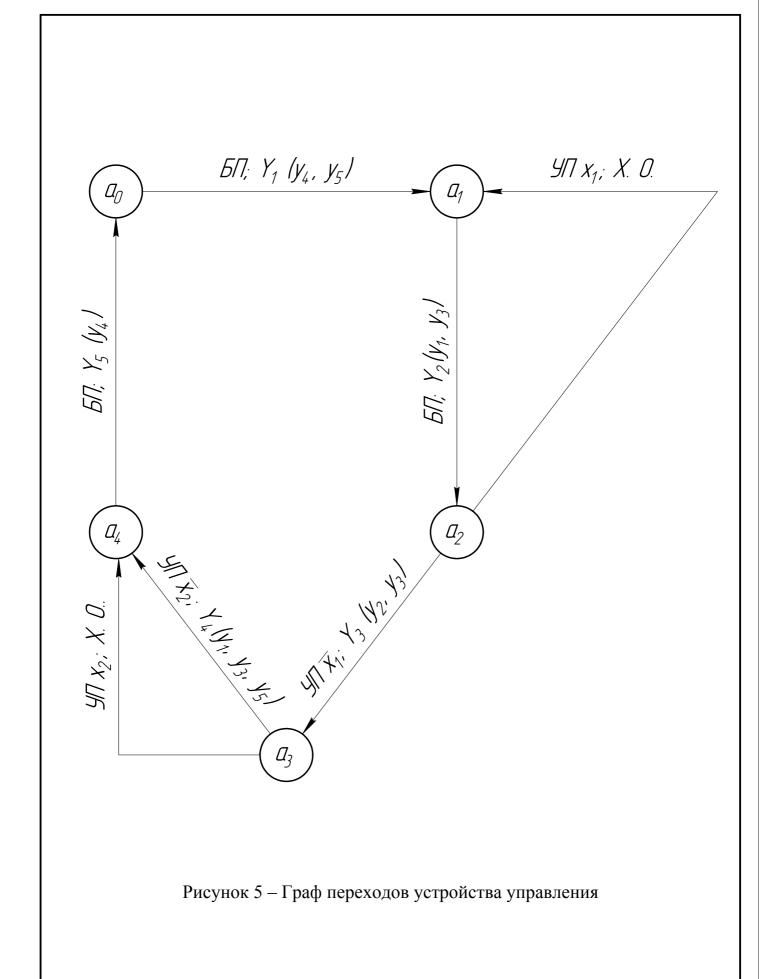

| 2.1 Построение графа устройства управления                       | 13 |

| 2.2 Таблица функционирования устройства управления               | 15 |

| 2.3 Запись логических выражений для комбинационной части схемы   | 18 |

| 2.4 Выбор элементной базы для построения принципиальной схемы    | 20 |

| ЗАКЛЮЧЕНИЕ                                                       | 24 |

| СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ                                 | 25 |

|                                                                  |    |

|  |  | · |  |  |

|--|--|---|--|--|

### 1 ТЕОРЕТИЧЕСКИЙ РАЗДЕЛ

#### 1.1 Структурная схема процессора со схемной логикой

При реализации вычислительных или управляющих процессов, в которых заранее известен алгоритм решения, прибегают к построению процессора со схемой логикой.

Процессор со схемой логикой состоит из двух устройств: управляющего и операционного (рис. 1).

Устройство управления, учитывая внутренние признаки (Q) (состояние процессора) и внешние признаки (x) алгоритма решаемой задачи, формирует управляющие сигналы (D) для перевода процессора в последующее состояние (Q) и для выполнения микроопераций (y) согласно заданного алгоритма.

Операционное устройство служит для выполнения под воздействием управляющих сигналов (у) математических, логических и других операций и формирование признаков (х).

Работа процессора синхронизируется с помощью генератора тактовых импульсов ГТИ, при этом частота формируемых генератором импульсов определяет быстродействие процессора.

|  | Ν. |  |  |

|--|----|--|--|

#### 1.2 Понятие цифрового автомата

Управляющее устройство процессора со схемой логикой представляет собой цифровой автомат, то есть логическое устройство, в котором помимо логических элементов имеются элементы памяти. Значения выходных сигналов такого устройства зависят не только от аргументов на входах в данный момент времени, но и от предыдущего состояния автомата, которое фиксируется элементами памяти. В качестве элементов памяти, как правило, используются триггеры. Каждое внутреннее состояние цифрового автомата определяется исходным состоянием триггеров и последовательностью входных сигналов, действующих на входах в данный момент времени.

В общем случае структурная схема управляющего устройства процессора со схемой логикой (цифрового автомата) состоит из трех узлов (рис.2): комбинационной схемы формирования выходных сигналов, комбинационной схемы сигналов управления триггерами и памяти.

На вход комбинационной схемы управления триггерами поступают комбинация входных сигналов  $x_1, x_2, ..., x_n$ , комбинации сигналов, отражающих состояние элементов памяти  $Q_1, Q_2, ..., Q_n$ . С учетом этих множеств сигналов комбинационная схема формирует серию сигналов  $D_1, D_2, ..., D_n$ , управляющих состоянием триггеров. Кодовые комбинации из состояния триггеров образуют внутренние состояние цифрового автомата, которое принято обозначать буквой а.

Комбинационная схема формирования выходных сигналов, формирует сигналы  $y_1, y_2, ..., y_n$ , управления операционным устройством процессора. Эти сигналы могут зависеть только от внутреннего состояния (Q). В этом случае устройство принято называть *автоматом Мура*. А если выходные сигналы зависят и от входных сигналов (x) то - *автоматом Мили*.

| M |

|---|

### 1.3 Анализ блок-схемы алгоритма команд

Последовательность действий устройства управления процессора со схемой логикой по формированию выходных сигналов и сигналов управления триггерами с учетом входных сигналов может быть задана с помощью алгоритма команд. Алгоритм фактически является формализованным представлением задачи по построению цифрового устройства, где определена группа выходных сигналов для инициализации устройств схемы.

Выполним построение устройства управления процессора со схемой логикой по заданному алгоритму команд (рис.3).

Алгоритм функционирования цифрового автомата состоит из пяти микрокоманд (Y), пяти микроопераций (y) и двух признаков (x).

Микрооперация — это элементарные действия (математические, логические, сдвиговые и т.д.), которые выполняет операционное устройство.

Микрокоманда — это совокупность микроопераций, которые выполняются в операционном устройстве в одном такте.

Признаки — это результаты реализуемых в операционном устройстве команд, которые могут влиять на ход реализации алгоритма.

В данном задаче имеется разветвленный вычислительный процесс, реализованный с помощью двух признаков  $x_1$  и  $x_2$ .

# 1.4 Определение состояний устройства управления и их кодирование

По алгоритму функционирования устройства управления процессора со схемой логикой (цифрового автомата) определяем и нумеруем устойчивые состояния «а».

Начало и конец алгоритма нумеруем одним состоянием  $a_0$ . Это означает, что в момент действия сигнала начальной установки и по окончанию процессов автомат переходит в состояние  $a_0$ . Далее состояния нумеруются после каждой микрокоманды по нарастанию.

|  | N | i |  |

|--|---|---|--|

Место на алгоритме, где автомат фиксирует внутреннее состояние, отмечаем символом «×» и проставляется буквенным обозначением «а» с соответствующим индексом.

На рис.3 проставим устойчивые состояния автомата. Как видно согласно заданного алгоритма количество устойчивых состояний пять:  $a_0$ ,  $a_1$ ,  $a_2$ ,  $a_3$ ,  $a_4$ .

Эти состояния необходимо закодировать, т.е. буквенному обозначению присвоить двоичный код.

Кодовые комбинации удобнее представлять в коде 8421. Соответствие кодовых комбинаций внутренним состояниям приведено в таблице 1.

Таблица 1 — Соответствие кодовых комбинаций внутренним состояниям

| Состояние автомата | Двоичный код |

|--------------------|--------------|

| $a_0$              | 000          |

| $a_1$              | 001          |

| $a_2$              | 010          |

| $a_3$              | 011          |

| $a_4$              | 100          |

Эти кодовые комбинации необходимо фиксировать в памяти устройства управления, которая представляется как регистр состояний и состоит из триггеров. Количество триггеров определяется числом состояний по соотношению

$$2^{n} \ge M \tag{1}$$

где n — количество триггеров, M — количество состояний.

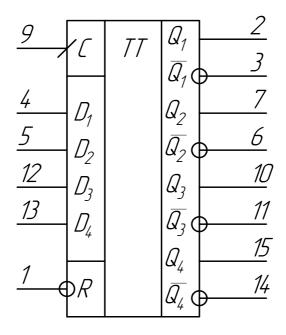

Таким образом, для данного автомата достаточно трех триггеров. В качестве триггеров необходимо использовать двухступенчатые триггеры. В этих триггерах одна ступень запоминает исходное состояние автомата, а в другой ступени происходит подготовка к переключению в новое состояние, что исключает *явление гонок*, то есть не одновременное переключение триг

геров, которое может привести к неверному функционированию цифрового автомата. Триггеры должны иметь входы предварительной установки, чтобы иметь возможность установить начальное состояние. Наиболее удобными для построения регистра состояний автомата являются двухступенчатые D-триггеры (рис. 4).

В данном триггере S, R — входы принудительной установки 1 или 0 соответственно, D — информационный вход, определяющий состояние триггера, С — динамический прямой синхронизирующий вход, Q и  $\overline{Q}$  - прямой и инверсный выходы триггера. Переключение триггера в состояние, определяющее входом D, происходит по фронту импульса поданного на вход C.

Для дальнейших расчетов приведем таблицу переходов D-триггера (таблица 2).

Таблица 2 – Переходы D-триггера.

| Переход           | D |

|-------------------|---|

| $0 \rightarrow 0$ | 0 |

| 0 → 1             | 1 |

| $1 \rightarrow 0$ | 0 |

| $1 \rightarrow 1$ | ] |

|  |     |  | 14 |

|--|-----|--|----|

|  | Ν . |  | 17 |

#### Заполнение третьей строки.

Исходное состояние  $a_2$ , которое согласно таблице 1 кодируется как  $Q_3=0,\ Q_2=1,\ Q_1=0.$  Из этого состояния автомат переходит в состояние  $a_1$ , которое согласно таблице 1 кодируется как  $Q_3=0,\ Q_2=0,\ Q_1=1.$  Этот переход условный по  $x_1=1$ , поэтому в столбец 9 ( $x_1$ ) ставим 1, а в столбец 10 ( $x_2$ ) ставим прочерк. При этом переходе должны быть сформированы входные сигналы  $y_1=0,\ y_2=0,\ y_3=0,\ y_4=0,\ y_5=0,\$  (столбцы 14-18).

Для обеспечения перехода из состояния  $a_2$  в  $a_1$  должны быть сформированы сигналы управления триггерами (таблица 2):  $D_3 = 0$  (переход  $0 \to 0$ ),  $D_2 = 0$  (переход  $1 \to 0$ ),  $D_1 = 1$  (переход  $0 \to 1$ ) (столбцы 11, 12, 13).

### Заполнение четвертой строки.

Исходное состояние  $a_2$ , которое согласно таблице 1 кодируется как  $Q_3=0,\ Q_2=1,\ Q_1=0.$  Из этого состояния автомат переходит в состояние  $a_3$ , которое согласно таблице 1 кодируется как  $Q_3=0,\ Q_2=1,\ Q_1=1.$  Этот переход условный по  $x_1=0$ , поэтому в столбец 9 ( $x_1$ ) ставим 0, а в столбец 10 ( $x_2$ ) ставим прочерк. При этом переходе должны быть сформированы входные сигналы  $y_1=0,\ y_2=1,\ y_3=1,\ y_4=0,\ y_5=0,$  (столбцы 14-18).

Для обеспечения перехода из состояния  $a_2$  в  $a_3$  должны быть сформированы сигналы управления триггерами (таблица 2):  $D_3 = 0$  (переход  $0 \to 0$ ),  $D_2 = 1$  (переход  $1 \to 1$ ),  $D_1 = 1$  (переход  $0 \to 1$ ) (столбцы 11, 12, 13).

#### Заполнение пятой строки.

Исходное состояние  $a_3$ , которое согласно таблице 1 кодируется как  $Q_3 = 0$ ,  $Q_2 = 1$ ,  $Q_1 = 1$ . Из этого состояния автомат переходит в состояние  $a_4$ , которое согласно таблице 1 кодируется как  $Q_3 = 1$ ,  $Q_2 = 0$ ,  $Q_1 = 0$ . Этот переход условный по  $x_2 = 1$ , поэтому в столбец 10 ( $x_2$ ) ставим 1, а в столбец 9 ( $x_1$ ) ставим прочерк. При этом переходе должны быть сформированы входные сигналы  $y_1 = 0$ ,  $y_2 = 0$ ,  $y_3 = 0$ ,  $y_4 = 0$ ,  $y_5 = 0$ , (столбцы 14-18).

| N |

|---|

Таблица 3 – Переходы и условия их реализации

|                | (              | Состо | энню  | е авто         | омата          | a     |       |                | овие<br>ехо- |       | игнал         |       |                       | Вь                    | іходн                 | ые         |                       |

|----------------|----------------|-------|-------|----------------|----------------|-------|-------|----------------|--------------|-------|---------------|-------|-----------------------|-----------------------|-----------------------|------------|-----------------------|

|                | Исхо           | дное  |       |                | Но             | вое   |       | _              | a<br>a       | -     | авле<br>ггера |       |                       | CF                    | ігнал                 | Ы          |                       |

| a              | Q <sub>3</sub> | $Q_2$ | $Q_1$ | a              | Q <sub>3</sub> | $Q_2$ | $Q_1$ | $\mathbf{x}_1$ | <b>X</b> 2   | $D_3$ | $D_2$         | $D_1$ | <b>y</b> <sub>1</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>3</sub> | <b>y</b> 4 | <b>y</b> <sub>5</sub> |

| 1              | 2              | 3     | 4     | 5              | 6              | 7     | 8     | 9              | 10           | 11    | 12            | 13    | 14                    | 15                    | 16                    | 17         | 18                    |

| $a_0$          | 0              | 0     | 0     | $a_1$          | 0              | 0     | 1     | _              | _            | 0     | 0             | 1     | 0                     | 0                     | 0                     | 1          | 1                     |

| $a_1$          | 0              | 0     | 1     | $a_2$          | 0              | 1     | 0     | _              | _            | 0     | 1             | 0     | 1                     | 0                     | 1                     | 0          | 0                     |

| $a_2$          | 0              | 1     | 0     | $a_1$          | 0              | 0     | 1     | 1              | _            | 0     | 0             | 1     | 0                     | 0                     | 0                     | 0          | 0                     |

| $a_2$          | 0              | 1     | 0     | $a_3$          | 0              | 1     | 1     | 0              | _            | 0     | 1             | 1     | 0                     | 1                     | 1                     | 0          | 0                     |

| a <sub>3</sub> | 0              | 1     | 1     | $a_4$          | 1              | 0     | 0     | _              | 1            | 1     | 0             | 0     | 0                     | 0                     | 0                     | 0          | 0                     |

| a <sub>3</sub> | 0              | 1     | 1     | a <sub>4</sub> | 1              | 0     | 0     | _              | 0            | 1     | 0             | 0     | 1                     | 0                     | 1                     | 0          | 1                     |

| $a_4$          | 1              | 0     | 0     | $a_0$          | 0              | 0     | 0     | _              | _            | 0     | 0             | 0     | 0                     | 0                     | 0                     | 1          | 0                     |

## 2.3 Запись логических выражений для комбинационной части схемы

После заполнения таблицы функционирования комбинационного узла автомата (таблица 3) переходим к записи логических выражений. У автомата Мили выходные сигналы и сигналы управления памятью являются функцией исходного состояния и признаков. При этом значения этих сигналов при их наличии (т.е. если они равны 1) определяются логическим умножением (конъюнкцией) исходного состояния и значения признака ( $\overline{x}$  если признак равен 0, x если признак равен 1).

Выходной сигнал  $y_1$  равен 1, если автомат находится в состоянии  $a_1$ , или в состоянии  $a_3$  и значение признака  $x_2=0$ . Это выражение в виде логической функции имеет вид

$$y_1 = a_1 \vee a_3 \cdot \overline{x_2} \tag{2}$$

|  |     |  | 12 |

|--|-----|--|----|

|  | l N |  | 10 |

Логические выражения (7, 9) можно упростить, применив закон склеивания. Окончательно логические выражения для комбинационной схемы имеют вид

Выходные сигналы

$$y_1 = a_1 \vee a_3 \cdot \overline{x_2} \tag{10}$$

$$y_2 = a_2 \cdot \overline{x_1} \tag{11}$$

$$y_3 = a_1 \vee a_2 \cdot \overline{x_1} \vee a_3 \cdot \overline{x_2} \tag{12}$$

$$y_4 = a_0 \vee a_4 \tag{13}$$

$$y_5 = a_0 \vee a_3 \cdot \overline{x_2} \tag{14}$$

Сигналы управления триггерами

$$D_1 = a_0 \vee a_2 \tag{15}$$

$$D_2 = a_1 \vee a_2 \cdot \overline{x_1} \tag{16}$$

$$D_3 = a_3 \tag{17}$$

# 2.4 Выбор элементной базы для построения принципиальной схемы

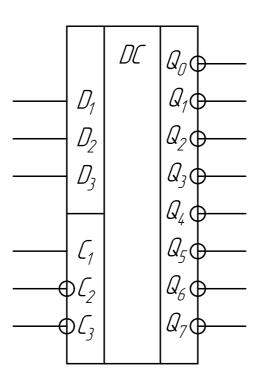

В результате анализа исходного алгоритма и выполненных расчетов, получаем логические выражения для построения принципиальной схемы цифрового автомата.

Построение схемы будем осуществлять на базе маломощных быстродействующих цифровых интегральных микросхем серии КР1533, предназначенных для организации высокоскоростного обмена и обработки цифровой информации.

В схеме должны присутствовать:

- двухступенчатые D триггеры, на базе которых строится регистр состояний

- дешифратор для преобразования кодовой комбинации триггеров в одиночный управляющий сигнал, соответствующий состоянию цифрового автомата

- логические элементы для реализации выражений выходных сигналов и сигналов управления триггерами.

|  | N    |  |

|--|------|--|

|  | IV . |  |

Рисунок 6 – Условно-графическое обозначение микросхемы К1533ТМ8

Рисунок 7 – Условно-графическое обозначение микросхемы К1533ИД7

|  | N     |  |   |

|--|-------|--|---|

|  | I I V |  | 1 |

#### ЗАКЛЮЧЕНИЕ

Исходя из блок-схемы алгоритма микрокоманд в курсовой работе построен граф устройства управления, таблица функционирования, записаны логические выражения для выходов.

На выбранной элементной базе построена принципиальная схема. Анализ работы на переходе показал, что схема работает в соответствии с таблицей функционирования.